(January 29, 1999)

Normal POST Codes

NOTE: EISA POST codes are typically output to port address 300h.

ISA POST codes are output to port address 80h.

Code(hex) Name Description

C0 Turn Off Chipset OEM Specific-Cache control cache

And CPU test

Processor Status (1FLAGS) Verification.

Tests the following processor status

flags: Carry, zero, sign, overflow,

The BIOS sets each flag, verifies

They are set, then turns each flag

off and verifies it is off.

Read/Write/Verify all CPU registers

except SS, SP, and BP with data

pattern FF and 00.

RAM must be periodically refreshed to

keep the memory from decaying. This

function ensures that the memory

refresh function is working properly.

C1 Memory Presence First block memory detect

OEM Specific-Test to size on-board

memory. Early chip set initialization

Memory presence test

OEM chip set routines

Clear low 64K of memory

Test first 64K memory.

C2 Early Memory OEM Specific- Board Initialization

Initialization

C3 Extend Memory OEM Specific- Turn on extended memory

DRAM select

Initialization

Cyrix CPU initialization

Cache initialization

1

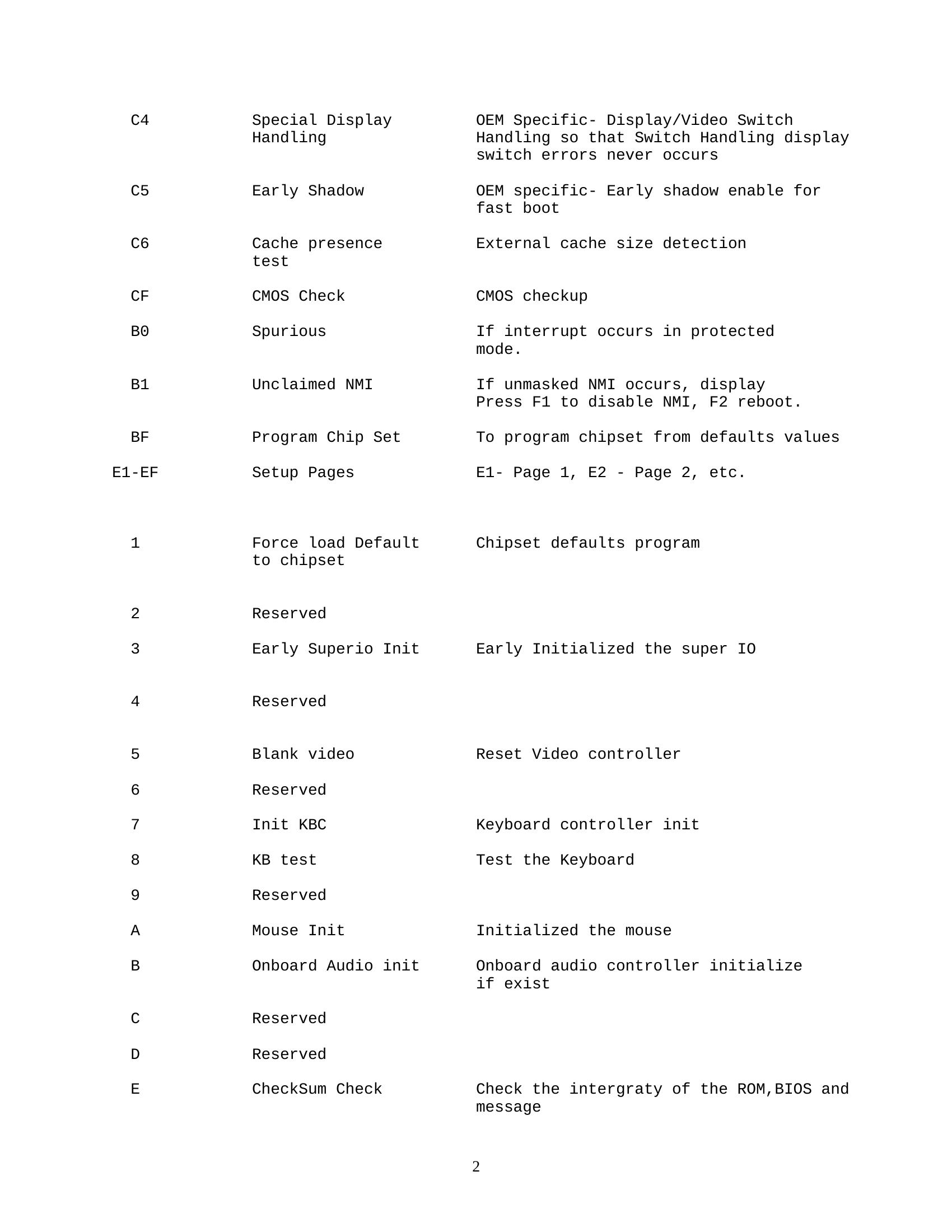

C4 Special Display OEM Specific- Display/Video Switch

Handling Handling so that Switch Handling display

switch errors never occurs

C5 Early Shadow OEM specific- Early shadow enable for

fast boot

C6 Cache presence External cache size detection

test

CF CMOS Check CMOS checkup

B0 Spurious If interrupt occurs in protected

mode.

B1 Unclaimed NMI If unmasked NMI occurs, display

Press F1 to disable NMI, F2 reboot.

BF Program Chip Set To program chipset from defaults values

E1-EF Setup Pages E1- Page 1, E2 – Page 2, etc.

1 Force load Default Chipset defaults program

to chipset

2 Reserved

3 Early Superio Init Early Initialized the super IO

4 Reserved

5 Blank video Reset Video controller

6 Reserved

7 Init KBC Keyboard controller init

8 KB test Test the Keyboard

9 Reserved

A Mouse Init Initialized the mouse

B Onboard Audio init Onboard audio controller initialize

if exist

C Reserved

D Reserved

E CheckSum Check Check the intergraty of the ROM,BIOS and

message

2

F Reserved

10 Auto detec EEPROM Check Flash type and copy flash

write/erase routines to 0F000h segments

11 Reserved

12 Cmos Check Check Cmos Circuitry and reset CMOS

13 Reserved

14 Chipset Default load Program the chipset registers with CMOS

values

15 Reserved

16 Clock Init Init onboard clock generator

17 Reserved

18 Identify the CPU Check the CPU ID and init L1/L2 cache

19 Reserved

1A Reserved

1B Setup Interrupt Initialize first 120 interrupt

Vector Table vectors with SPURIOUS_INT_HDLR and

initialize

INT 00h-1Fh according to INT_TBL

1C Reserved

1D Early PM Init First step initialize if single CPU

onboard

1E Reserved

1F Re-initial KB Re-init KB

20 Reserved

21 HPM init If support HPM, HPM get initialized here

22 Reserved

23 Test CMOS Verifies CMOS is working correctly,

Interface and detects bad battery. If failed,load CMOS

Battery Status defaults and load into chipset

24 Reserved

25 Reserved

26 Reserved

3

27 KBC final Init Final Initial KBC and setup BIOS data

area

28 Reserved

29 Initialize Video Read CMOS location 14h to find out

Interface type of video in use.

Detect and Initialize Video Adapter.

2A Reserved

2B Reserved

2C Reserved

2D Video memory test Test video memory, write sign-on

message to screen.

2E Reserved Setup shadow RAM – Enable shadow

according to Setup.

2F Reserved

30 Reserved

31 Reserved

32 Reserved

33 PS2 Mouse setup Setup PS2 Mouse and reset KB

34 Reserved

35 Test DMA Test DMA channel 0

Controller 0

36 Reserved

37 Test DMA Test DMA channel 1

Controller 1

38 Reserved

39 Test DMA Page Test DMA Page Registers.

Registers

3A Reserved

3B Reserved

3C Test Timer Test 8254 Timer 0 Counter 2.

Counter 2

4

3D Reserved

3E Test 8259-1 Mask Verify 8259 Channel 1 masked

Bits interrupts by alternately turning off

and on the interrupt lines.

3F Reserved

40 Test 8259-2 Mask Verify 8259 Channel 2 masked

Bits interrupts by alternately turning off

and on the interrupt lines.

41 Reserved

42 Reserved

43 Test Stuck Turn off interrupts then verify no

8259’s Interrupt interrupt mask register is on.

Bits

Test 8259 Force an interrupt and verify the

Interrupt interrupt occurred.

Functionality

44 Reserved

45 Reserved

46 Reserved

47 Set EISA Mode If EISA non-volatile memory checksum

is good, execute EISA initialization.

If not, execute ISA tests an clear

EISA mode flag.

48 Reserved

49 Size Base and Size base memory from 256K to 640K

Extended Memory and extended memory above 1MB.

4A Reserved

4B Reserved

4C Reserved

4D Reserved

4E Test Base and Test base memory from 256K to 640K

Extended Memory and extended memory above 1MB using

various patterns.

5

NOTE: This test is skipped in EISA

mode and can be skipped with ESC key

in ISA mode.

4F Reserved

50 USB init Initialize USB controller

51 Reserved

52 Memory Test Test all memory of memory above 1MB

using Virtual 8086 mode,

page mode and clear the memory

53 Reserved

54 Reserved

55 CPU display Detect CPU speed and display

CPU vendor specific version string

and turn on all necessary CPU features

56 Reserved

57 PnP Init Display PnP logo and PnP early init

58 Reserved

59 Setup Virus Setup virus protect according to

Protect Setup

5A Reserved

5B Awdflash Load If required, will auto load

Awdflash.exe in POST

5C Reserved

5D Onboard I/O Init Initializing onboard superIO

5E Reserved

5F Reserved

60 Setup enable Display setup message and enable setup

functions

61 Reserved

62 Reserved

6

63 Initialize & Detect if mouse is present,

Install Mouse initialize mouse, install interrupt

vectors.

64 Reserved

65 PS2 Mouse special Special treatment to PS2 Mouse port

66 Reserved

67 ACPI init ACPI sub-system initializing

68 Reserved

69 Setup Cache Initialize cache controller.

Controller

6A Reserved

6B Setup Entering Enter setup check and auto-

configuration check up

6C Reserved

6D Initialize Initialize floppy disk drive

Floppy Drive & controller and any drives.

Controller

6E Reserved

6F FDD install Install FDD and setup BIOS data area

parameters

70 Reserved

71 Reserved

72 Reserved

73 Initialize Hard Initialize hard drive controller and

Drive & any drives.

Controller

74 Reserved

75 Install HDD IDE device detection and install

76 Reserved

77 Detect & Initialize any serial and parallel

Initialize ports (also game port).

Serial/Parallel

7

Ports

78 Reserved

79 Reserved

7A Detect & Initialize math coprocessor.

Initialize Math

Coprocessor

7B Reserved

7C HDD Check for Write HDD check out

protection

7D Reserved

7E Reserved

7F POST error check Check POST error and display them

and ask for user intervention

80 Reserved

81 Reserved

82 Security Check Ask password security (optional).

83 Write CMOS Write all CMOS values back to RAM and

clear screen.

84 Pre-boot Enable Enable parity checker

Enable NMI, Enable cache before boot.

85 Initialize Initialize any option ROMs present

Option ROMs from C8000h to EFFFFh.

NOTE: When FSCAN option is enabled,

ROMs initialize from C8000h to

F7FFFh.

86 Reserved

87 Reserved

88 Reserved

89 Reserved

8A Reserved

8B Reserved

8C Reserved

8

8D Reserved

8E Reserved

8F Reserved

90 Reserved

91 Reserved

92 Reserved

93 Boot Medium detection Read and store boot partition head and

cylinders values in RAM

94 Final Init Final init for last micro details

before boot

95 Special KBC patch Set system speed for boot

Setup NumLock status according to

Setup

96 Boot Attempt Set low stack

Boot via INT 19h.

FF Boot

Quick POST Codes

65 Init onboard device Early Initialized the super IO

Reset Video controller

Keyboard controller init

Test the Keyboard Initialized the

mouse Onboard audio controller

initialize if exist. Check the

intergraty of the ROM, BIOS and

message Check Flash type and copy

flash write/erase routines to 0F000h

segments Check Cmos Circuitry and

reset CMOS Program the chipset

registers with CMOS values

Init onboard clock generator

66 Early Sytem setup Check the CPU ID and init L1/L2 cache

Initialize first 120 interrupt

vectors with SPURIOUS_INT_HDLR and

9

initialize

INT 00h-1Fh according to INT_TBL

First step initialize if single CPU

onboard. Re-init KB

If support HPM, HPM get initialized

here

67 KBC and CMOS Init Verifies CMOS is working correctly,

detects bad battery.If failed, load

CMOS defaults and load into chipset

Final Initial KBC and setup BIOS data

area.

68 Video Init Read CMOS location 14h to find out

type of video in use.

Detect and Initialize Video Adapter.

Test video memory, write sign-on

message to screen.

Setup shadow RAM – Enable shadow

according to Setup.

69 8259 Init Init 8259 channel 1 and mask IRQ 9

6A Memory test Quick Memory Test

6B CPU Detect and IO init Detect CPU speed and display

CPU vendor specific version string

and turn on all necessary CPU features

Display PnP logo and PnP early init

Setup virus protect according to

Setup. If required, will auto load

Awdflash.exe in POST

Initializing onboard superIO

6C Reserved

6D Reserved

6E Reserved

6F Reserved

70 Setup Init Display setup message and enable setup

functions Detect if mouse is present,

initialize mouse, install interrupt

vectors. Special treatment to PS2

Mouse port

ACPI sub-system initializing

71 Setup Cache Initialize cache controller.

Controller

72 Install FDD Enter setup check and auto-

10

configuration check up

Initialize floppy disk drive

controller and any drives.

Install FDD and setup BIOS data area

parameters

73 Install HDD Initialize hard drive controller and

any drives.

IDE device detection and install

Initialize any serial and parallel

ports (also game port).

74 Detect & Initialize math coprocessor.

Initialize Math

Coprocessor

75 HDD Check for Write HDD check out

protection

76 Reserved

77 Display POST error Check POST error and display them

and ask for user intervention

Ask password security (optional).

78 CMOS and Option ROM Init Write all CMOS values back to RAM and

clear screen.

Enable parity checker

Enable NMI, Enable cache before boot.

Initialize any option ROMs present

from C8000h to EFFFFh.

NOTE: When FSCAN option is enabled,

ROMs initialize from C8000h to

F7FFFh.

79 Reserved

7A Reserved

7B Reserved

7C Reserved

7D Boot Medium detection Read and store boot partition head and

cylinders values in RAM

7E Final Init Final init for last micro details

before boot

7F Special KBC patch Set system speed for boot

Setup NumLock status according to

Setup

11

80 Boot Attempt Set low stack

Boot via INT 19h.

FF Boot

S4 POST Codes

5A Early Chipset Init Early Initialized the super IO

Reset Video controller

Keyboard controller init

Test the Keyboard

Initilized the mouse

5B Cmos Check Check Cmos Circuitry and reset CMOS

5C Chipset default Prog Program the chipset registers with

CMOS values. Init onboard clock

generator

5D Identify the CPU Check the CPU ID and init L1/L2 cache

5E Setup Interrupt Initialize first 120 interrupt

Vector Table vectors with SPURIOUS_INT_HDLR and

INT 00h-1Fh according to INT_TBL

First step initialize if single CPU

Onboard. Re-init KB

If support HPM, HPM get initialized

Here.

5F Test CMOS Verifies CMOS is working correctly,

Interface and detects bad battery.If failed, load

Battery status CMOS defaults and load into chipset

60 KBC final Init Final Initial KBC and setup BIOS data

area

61 Initialize Video Read CMOS location 14h to find out

Interface type of video in use.

Detect and Initialize Video Adapter.

62 Video memory test Test video memory, write sign-on

message to screen.

Setup shadow RAM – Enable shadow

according to Setup.

12

63 Setup PS2 mouse and Setup PS2 Mouse and reset KB

test DMA Test DMA channel 0

64 Test 8259 Test 8259 channel 1 and mask IRQ 9

65 Init Boot Device Detect if mouse is present,

initialize mouse, install interrupt

vectors.

Special treatment to PS2 Mouse port

ACPI sub-system initializing

Initialize cache controller.

66 Install Boot Devices Enter setup check and auto-

configuration check up

Initialize floppy disk drive

controller and any drives.

Install FDD and setup BIOS data area

Parameters Initialize hard drive

controller and any drives.

IDE device detection and install

67 Cache Init Cache init and USB init

68 PM init PM initialization

69 PM final Init and issue SMI Final init Before resume

FF Full on

BootBlock POST Codes

1 Base memory test Clear base memory area (0000:0000–9000:ffffh)

5 KB init Initialized KBC

12 Install interrupt vectors Install int. vector (0-77), and initialized 00-1fh to their

proper place

0D Init Video Video initializing

41 Init FDD Scan floppy and media capacity for onboard superIO

FF Boot Load boot sector

13

Proprietary Notice and Disclaimer

Unless otherwise noted, this document and the information herein disclosed are proprietary to Phoenix Technologies

Ltd. (Phoenix). Any person or entity to whom this document is furnished or who otherwise has possession thereof, by

acceptance agrees that it will not be copied or reproduced in whole or in part, nor used in any manner except to meet

the purposes for which it was delivered.

The information in this document is subject to change without notice, and should not be considered as a commitment

by Phoenix. Although Phoenix will make every effort to inform users of substantive errors, Phoenix disclaims all

liability for any loss or damage resulting from the use of this document or any hardware or software described herein,

including without limitation contingent, special, or incidental liability.

MedallionBIOS is a trademark of Phoenix Technologies Ltd.

Award Software International and the Award logo are registered trademarks of Award Software International Inc. a

wholly owned subsidiaries of Phoenix Technologies Ltd.

All other products and brand names are trademarks and registered trademarks of their respective companies.

14